#include <SdramSpdDdr3.h>

Public Attributes | |

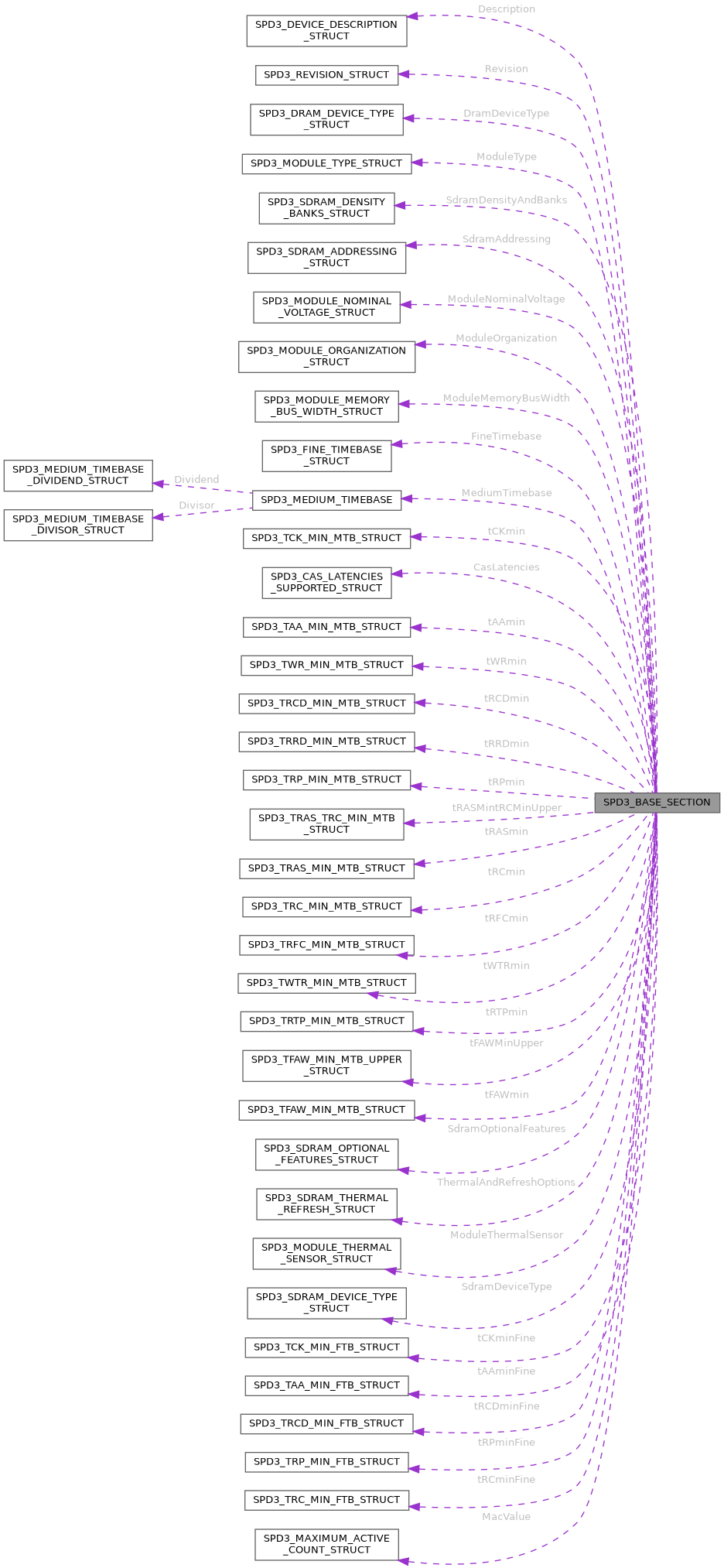

| SPD3_DEVICE_DESCRIPTION_STRUCT | Description |

| 0 Number of Serial PD Bytes Written / SPD Device Size / CRC Coverage 1, 2 | |

| SPD3_REVISION_STRUCT | Revision |

| 1 SPD Revision | |

| SPD3_DRAM_DEVICE_TYPE_STRUCT | DramDeviceType |

| 2 DRAM Device Type | |

| SPD3_MODULE_TYPE_STRUCT | ModuleType |

| 3 Module Type | |

| SPD3_SDRAM_DENSITY_BANKS_STRUCT | SdramDensityAndBanks |

| 4 SDRAM Density and Banks | |

| SPD3_SDRAM_ADDRESSING_STRUCT | SdramAddressing |

| 5 SDRAM Addressing | |

| SPD3_MODULE_NOMINAL_VOLTAGE_STRUCT | ModuleNominalVoltage |

| 6 Module Nominal Voltage, VDD | |

| SPD3_MODULE_ORGANIZATION_STRUCT | ModuleOrganization |

| 7 Module Organization | |

| SPD3_MODULE_MEMORY_BUS_WIDTH_STRUCT | ModuleMemoryBusWidth |

| 8 Module Memory Bus Width | |

| SPD3_FINE_TIMEBASE_STRUCT | FineTimebase |

| 9 Fine Timebase (FTB) Dividend / Divisor | |

| SPD3_MEDIUM_TIMEBASE | MediumTimebase |

| 10-11 Medium Timebase (MTB) Dividend | |

| SPD3_TCK_MIN_MTB_STRUCT | tCKmin |

| 12 SDRAM Minimum Cycle Time (tCKmin) | |

| UINT8 | Reserved0 |

| 13 Reserved | |

| SPD3_CAS_LATENCIES_SUPPORTED_STRUCT | CasLatencies |

| 14-15 CAS Latencies Supported | |

| SPD3_TAA_MIN_MTB_STRUCT | tAAmin |

| 16 Minimum CAS Latency Time (tAAmin) | |

| SPD3_TWR_MIN_MTB_STRUCT | tWRmin |

| 17 Minimum Write Recovery Time (tWRmin) | |

| SPD3_TRCD_MIN_MTB_STRUCT | tRCDmin |

| 18 Minimum RAS# to CAS# Delay Time (tRCDmin) | |

| SPD3_TRRD_MIN_MTB_STRUCT | tRRDmin |

| 19 Minimum Row Active to Row Active Delay Time (tRRDmin) | |

| SPD3_TRP_MIN_MTB_STRUCT | tRPmin |

| 20 Minimum Row Precharge Delay Time (tRPmin) | |

| SPD3_TRAS_TRC_MIN_MTB_STRUCT | tRASMintRCMinUpper |

| 21 Upper Nibbles for tRAS and tRC | |

| SPD3_TRAS_MIN_MTB_STRUCT | tRASmin |

| 22 Minimum Active to Precharge Delay Time (tRASmin), Least Significant Byte | |

| SPD3_TRC_MIN_MTB_STRUCT | tRCmin |

| 23 Minimum Active to Active/Refresh Delay Time (tRCmin), Least Significant Byte | |

| SPD3_TRFC_MIN_MTB_STRUCT | tRFCmin |

| 24-25 Minimum Refresh Recovery Delay Time (tRFCmin) | |

| SPD3_TWTR_MIN_MTB_STRUCT | tWTRmin |

| 26 Minimum Internal Write to Read Command Delay Time (tWTRmin) | |

| SPD3_TRTP_MIN_MTB_STRUCT | tRTPmin |

| 27 Minimum Internal Read to Precharge Command Delay Time (tRTPmin) | |

| SPD3_TFAW_MIN_MTB_UPPER_STRUCT | tFAWMinUpper |

| 28 Upper Nibble for tFAW | |

| SPD3_TFAW_MIN_MTB_STRUCT | tFAWmin |

| 29 Minimum Four Activate Window Delay Time (tFAWmin) | |

| SPD3_SDRAM_OPTIONAL_FEATURES_STRUCT | SdramOptionalFeatures |

| 30 SDRAM Optional Features | |

| SPD3_SDRAM_THERMAL_REFRESH_STRUCT | ThermalAndRefreshOptions |

| 31 SDRAM Thermal And Refresh Options | |

| SPD3_MODULE_THERMAL_SENSOR_STRUCT | ModuleThermalSensor |

| 32 Module Thermal Sensor | |

| SPD3_SDRAM_DEVICE_TYPE_STRUCT | SdramDeviceType |

| 33 SDRAM Device Type | |

| SPD3_TCK_MIN_FTB_STRUCT | tCKminFine |

| 34 Fine Offset for SDRAM Minimum Cycle Time (tCKmin) | |

| SPD3_TAA_MIN_FTB_STRUCT | tAAminFine |

| 35 Fine Offset for Minimum CAS Latency Time (tAAmin) | |

| SPD3_TRCD_MIN_FTB_STRUCT | tRCDminFine |

| 36 Fine Offset for Minimum RAS# to CAS# Delay Time (tRCDmin) | |

| SPD3_TRP_MIN_FTB_STRUCT | tRPminFine |

| 37 Minimum Row Precharge Delay Time (tRPmin) | |

| SPD3_TRC_MIN_FTB_STRUCT | tRCminFine |

| 38 Fine Offset for Minimum Active to Active/Refresh Delay Time (tRCmin) | |

| UINT8 | Reserved1 [40 - 39+1] |

| 39 - 40 Reserved | |

| SPD3_MAXIMUM_ACTIVE_COUNT_STRUCT | MacValue |

| 41 SDRAM Maximum Active Count (MAC) Value | |

| UINT8 | Reserved2 [59 - 42+1] |

| 42 - 59 Reserved | |

Member Data Documentation

◆ CasLatencies

| SPD3_CAS_LATENCIES_SUPPORTED_STRUCT SPD3_BASE_SECTION::CasLatencies |

14-15 CAS Latencies Supported

◆ Description

| SPD3_DEVICE_DESCRIPTION_STRUCT SPD3_BASE_SECTION::Description |

0 Number of Serial PD Bytes Written / SPD Device Size / CRC Coverage 1, 2

◆ DramDeviceType

| SPD3_DRAM_DEVICE_TYPE_STRUCT SPD3_BASE_SECTION::DramDeviceType |

2 DRAM Device Type

◆ FineTimebase

| SPD3_FINE_TIMEBASE_STRUCT SPD3_BASE_SECTION::FineTimebase |

9 Fine Timebase (FTB) Dividend / Divisor

◆ MacValue

| SPD3_MAXIMUM_ACTIVE_COUNT_STRUCT SPD3_BASE_SECTION::MacValue |

41 SDRAM Maximum Active Count (MAC) Value

◆ MediumTimebase

| SPD3_MEDIUM_TIMEBASE SPD3_BASE_SECTION::MediumTimebase |

10-11 Medium Timebase (MTB) Dividend

◆ ModuleMemoryBusWidth

| SPD3_MODULE_MEMORY_BUS_WIDTH_STRUCT SPD3_BASE_SECTION::ModuleMemoryBusWidth |

8 Module Memory Bus Width

◆ ModuleNominalVoltage

| SPD3_MODULE_NOMINAL_VOLTAGE_STRUCT SPD3_BASE_SECTION::ModuleNominalVoltage |

6 Module Nominal Voltage, VDD

◆ ModuleOrganization

| SPD3_MODULE_ORGANIZATION_STRUCT SPD3_BASE_SECTION::ModuleOrganization |

7 Module Organization

◆ ModuleThermalSensor

| SPD3_MODULE_THERMAL_SENSOR_STRUCT SPD3_BASE_SECTION::ModuleThermalSensor |

32 Module Thermal Sensor

◆ ModuleType

| SPD3_MODULE_TYPE_STRUCT SPD3_BASE_SECTION::ModuleType |

3 Module Type

◆ Reserved0

| UINT8 SPD3_BASE_SECTION::Reserved0 |

13 Reserved

◆ Reserved1

| UINT8 SPD3_BASE_SECTION::Reserved1[40 - 39+1] |

39 - 40 Reserved

◆ Reserved2

| UINT8 SPD3_BASE_SECTION::Reserved2[59 - 42+1] |

42 - 59 Reserved

◆ Revision

| SPD3_REVISION_STRUCT SPD3_BASE_SECTION::Revision |

1 SPD Revision

◆ SdramAddressing

| SPD3_SDRAM_ADDRESSING_STRUCT SPD3_BASE_SECTION::SdramAddressing |

5 SDRAM Addressing

◆ SdramDensityAndBanks

| SPD3_SDRAM_DENSITY_BANKS_STRUCT SPD3_BASE_SECTION::SdramDensityAndBanks |

4 SDRAM Density and Banks

◆ SdramDeviceType

| SPD3_SDRAM_DEVICE_TYPE_STRUCT SPD3_BASE_SECTION::SdramDeviceType |

33 SDRAM Device Type

◆ SdramOptionalFeatures

| SPD3_SDRAM_OPTIONAL_FEATURES_STRUCT SPD3_BASE_SECTION::SdramOptionalFeatures |

30 SDRAM Optional Features

◆ tAAmin

| SPD3_TAA_MIN_MTB_STRUCT SPD3_BASE_SECTION::tAAmin |

16 Minimum CAS Latency Time (tAAmin)

◆ tAAminFine

| SPD3_TAA_MIN_FTB_STRUCT SPD3_BASE_SECTION::tAAminFine |

35 Fine Offset for Minimum CAS Latency Time (tAAmin)

◆ tCKmin

| SPD3_TCK_MIN_MTB_STRUCT SPD3_BASE_SECTION::tCKmin |

12 SDRAM Minimum Cycle Time (tCKmin)

◆ tCKminFine

| SPD3_TCK_MIN_FTB_STRUCT SPD3_BASE_SECTION::tCKminFine |

34 Fine Offset for SDRAM Minimum Cycle Time (tCKmin)

◆ tFAWmin

| SPD3_TFAW_MIN_MTB_STRUCT SPD3_BASE_SECTION::tFAWmin |

29 Minimum Four Activate Window Delay Time (tFAWmin)

◆ tFAWMinUpper

| SPD3_TFAW_MIN_MTB_UPPER_STRUCT SPD3_BASE_SECTION::tFAWMinUpper |

28 Upper Nibble for tFAW

◆ ThermalAndRefreshOptions

| SPD3_SDRAM_THERMAL_REFRESH_STRUCT SPD3_BASE_SECTION::ThermalAndRefreshOptions |

31 SDRAM Thermal And Refresh Options

◆ tRASmin

| SPD3_TRAS_MIN_MTB_STRUCT SPD3_BASE_SECTION::tRASmin |

22 Minimum Active to Precharge Delay Time (tRASmin), Least Significant Byte

◆ tRASMintRCMinUpper

| SPD3_TRAS_TRC_MIN_MTB_STRUCT SPD3_BASE_SECTION::tRASMintRCMinUpper |

21 Upper Nibbles for tRAS and tRC

◆ tRCDmin

| SPD3_TRCD_MIN_MTB_STRUCT SPD3_BASE_SECTION::tRCDmin |

18 Minimum RAS# to CAS# Delay Time (tRCDmin)

◆ tRCDminFine

| SPD3_TRCD_MIN_FTB_STRUCT SPD3_BASE_SECTION::tRCDminFine |

36 Fine Offset for Minimum RAS# to CAS# Delay Time (tRCDmin)

◆ tRCmin

| SPD3_TRC_MIN_MTB_STRUCT SPD3_BASE_SECTION::tRCmin |

23 Minimum Active to Active/Refresh Delay Time (tRCmin), Least Significant Byte

◆ tRCminFine

| SPD3_TRC_MIN_FTB_STRUCT SPD3_BASE_SECTION::tRCminFine |

38 Fine Offset for Minimum Active to Active/Refresh Delay Time (tRCmin)

◆ tRFCmin

| SPD3_TRFC_MIN_MTB_STRUCT SPD3_BASE_SECTION::tRFCmin |

24-25 Minimum Refresh Recovery Delay Time (tRFCmin)

◆ tRPmin

| SPD3_TRP_MIN_MTB_STRUCT SPD3_BASE_SECTION::tRPmin |

20 Minimum Row Precharge Delay Time (tRPmin)

◆ tRPminFine

| SPD3_TRP_MIN_FTB_STRUCT SPD3_BASE_SECTION::tRPminFine |

37 Minimum Row Precharge Delay Time (tRPmin)

◆ tRRDmin

| SPD3_TRRD_MIN_MTB_STRUCT SPD3_BASE_SECTION::tRRDmin |

19 Minimum Row Active to Row Active Delay Time (tRRDmin)

◆ tRTPmin

| SPD3_TRTP_MIN_MTB_STRUCT SPD3_BASE_SECTION::tRTPmin |

27 Minimum Internal Read to Precharge Command Delay Time (tRTPmin)

◆ tWRmin

| SPD3_TWR_MIN_MTB_STRUCT SPD3_BASE_SECTION::tWRmin |

17 Minimum Write Recovery Time (tWRmin)

◆ tWTRmin

| SPD3_TWTR_MIN_MTB_STRUCT SPD3_BASE_SECTION::tWTRmin |

26 Minimum Internal Write to Read Command Delay Time (tWTRmin)

The documentation for this struct was generated from the following file:

- XenevaOS/Boot/include/IndustryStandard/SdramSpdDdr3.h