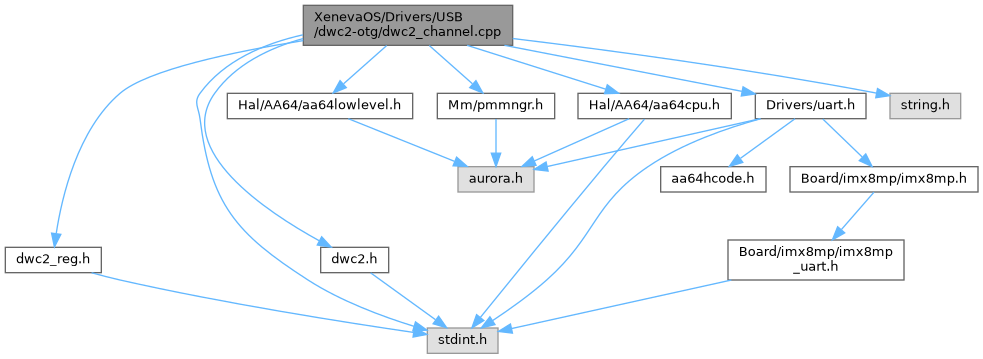

#include "dwc2_reg.h"#include <stdint.h>#include "dwc2.h"#include <Hal/AA64/aa64lowlevel.h>#include <Hal/AA64/aa64cpu.h>#include <Mm/pmmngr.h>#include <Drivers/uart.h>#include <string.h>

Functions | |

| uint64_t | dwc2_get_base () |

| void | dwc2_reset_channel (dwc2_core_regs *regs, uint8_t ch) |

| void | dwc2_start_channel (struct dwc2_core_regs *regs, dwc2_usb_endpoint_t *ep, uint8_t ch, uint8_t is_in, uint8_t ep_type, uint8_t pid, void *dma, uint32_t length, uint32_t pack_count, uint8_t is_odd_frame) |

| dwc2_start_channel – allocates a channel | |

| void | dwc2_start_transaction (struct dwc2_core_regs *regs, uint8_t ch, void *dma, uint32_t length, uint32_t pack_count, uint8_t pid, uint8_t is_odd_frame) |

| int | dwc2_wait_channel (struct dwc2_core_regs *regs, int ch) |

| void | dwc2_control_transfer (struct dwc2_core_regs *regs, dwc2_usb_endpoint_t *ep, uint8_t bmRequestType, uint8_t b_request, uint16_t wValue, uint16_t wIndex, void *data, uint16_t wLength) |

| void | dwc2_handle_channel_interrupt (dwc2_core_regs *regs, int ch) |

| dwc2_handle_channel_interrupt – handle channel interrupts here | |

| void | dwc2_interrupt_transfer (dwc2_core_regs *regs, dwc2_usb_endpoint_t *ep, void *intbuf, uint8_t ch, uint32_t odd, uint8_t pid) |

Variables | |

| uint8_t | port_changed |

Detailed Description

BSD 2-Clause License

Copyright (c) 2022-2026, Manas Kamal Choudhury All rights reserved.

Redistribution and use in source and binary forms, with or without modification, are permitted provided that the following conditions are met:

- Redistributions of source code must retain the above copyright notice, this list of conditions and the following disclaimer.

- Redistributions in binary form must reproduce the above copyright notice, this list of conditions and the following disclaimer in the documentation and/or other materials provided with the distribution.

THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT HOLDER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

Function Documentation

◆ dwc2_control_transfer()

| void dwc2_control_transfer | ( | struct dwc2_core_regs * | regs, |

| dwc2_usb_endpoint_t * | ep, | ||

| uint8_t | bmRequestType, | ||

| uint8_t | b_request, | ||

| uint16_t | wValue, | ||

| uint16_t | wIndex, | ||

| void * | data, | ||

| uint16_t | wLength | ||

| ) |

setup the status stage

free up the channel

◆ dwc2_get_base()

|

extern |

◆ dwc2_handle_channel_interrupt()

| void dwc2_handle_channel_interrupt | ( | dwc2_core_regs * | regs, |

| int | ch | ||

| ) |

dwc2_handle_channel_interrupt – handle channel interrupts here

- Parameters

-

regs – Pointer to dwc2 core registers ch – channel numbers

W1C

◆ dwc2_interrupt_transfer()

| void dwc2_interrupt_transfer | ( | dwc2_core_regs * | regs, |

| dwc2_usb_endpoint_t * | ep, | ||

| void * | intbuf, | ||

| uint8_t | ch, | ||

| uint32_t | odd, | ||

| uint8_t | pid | ||

| ) |

◆ dwc2_reset_channel()

| void dwc2_reset_channel | ( | dwc2_core_regs * | regs, |

| uint8_t | ch | ||

| ) |

◆ dwc2_start_channel()

| void dwc2_start_channel | ( | struct dwc2_core_regs * | regs, |

| dwc2_usb_endpoint_t * | ep, | ||

| uint8_t | ch, | ||

| uint8_t | is_in, | ||

| uint8_t | ep_type, | ||

| uint8_t | pid, | ||

| void * | dma, | ||

| uint32_t | length, | ||

| uint32_t | pack_count, | ||

| uint8_t | is_odd_frame | ||

| ) |

dwc2_start_channel – allocates a channel

clear all pending interrupts

now set transfer size

now set the dma address

◆ dwc2_start_transaction()

| void dwc2_start_transaction | ( | struct dwc2_core_regs * | regs, |

| uint8_t | ch, | ||

| void * | dma, | ||

| uint32_t | length, | ||

| uint32_t | pack_count, | ||

| uint8_t | pid, | ||

| uint8_t | is_odd_frame | ||

| ) |

now set transfer size

now enable the channel

◆ dwc2_wait_channel()

| int dwc2_wait_channel | ( | struct dwc2_core_regs * | regs, |

| int | ch | ||

| ) |

Variable Documentation

◆ port_changed

|

extern |