#include <SdramSpdDdr3.h>

Member Data Documentation

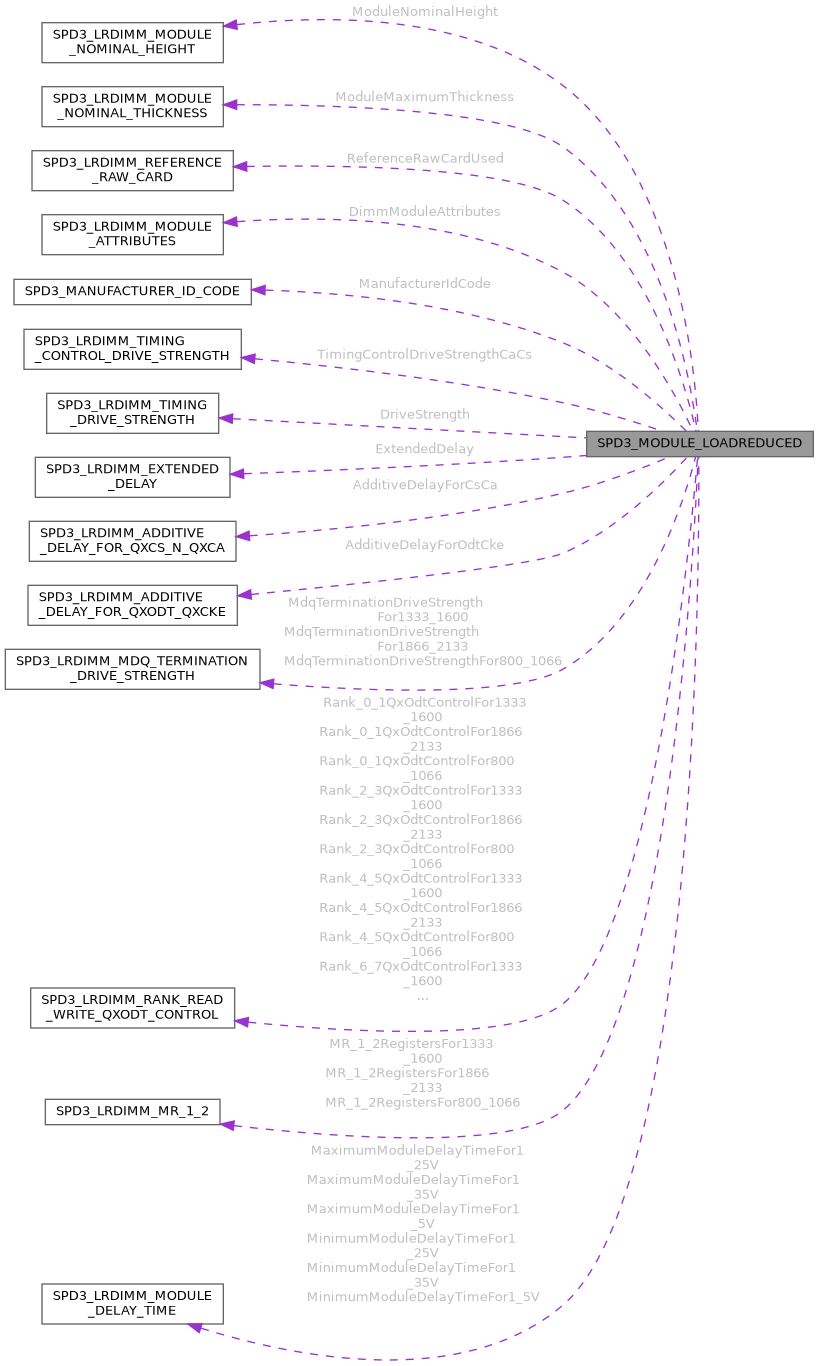

◆ AdditiveDelayForCsCa

| SPD3_LRDIMM_ADDITIVE_DELAY_FOR_QXCS_N_QXCA SPD3_MODULE_LOADREDUCED::AdditiveDelayForCsCa |

70 F1RC13 / F1RC12 - Additive Delay for CS and CA

◆ AdditiveDelayForOdtCke

| SPD3_LRDIMM_ADDITIVE_DELAY_FOR_QXODT_QXCKE SPD3_MODULE_LOADREDUCED::AdditiveDelayForOdtCke |

71 F1RC15 / F1RC14 - Additive Delay for ODT & CKE

◆ DimmModuleAttributes

| SPD3_LRDIMM_MODULE_ATTRIBUTES SPD3_MODULE_LOADREDUCED::DimmModuleAttributes |

63 Module Attributes

◆ DriveStrength

| SPD3_LRDIMM_TIMING_DRIVE_STRENGTH SPD3_MODULE_LOADREDUCED::DriveStrength |

68 F0RC5 / F0RC4 - Drive Strength, ODT & CKE and Y

◆ ExtendedDelay

| SPD3_LRDIMM_EXTENDED_DELAY SPD3_MODULE_LOADREDUCED::ExtendedDelay |

69 F1RC11 / F1RC8 - Extended Delay for Y, CS and ODT & CKE

◆ ManufacturerIdCode

| SPD3_MANUFACTURER_ID_CODE SPD3_MODULE_LOADREDUCED::ManufacturerIdCode |

65-66 Memory Buffer Manufacturer ID Code

◆ MaximumModuleDelayTimeFor1_25V

| SPD3_LRDIMM_MODULE_DELAY_TIME SPD3_MODULE_LOADREDUCED::MaximumModuleDelayTimeFor1_25V |

95 Maximum Module Delay Time for 1.25 V

◆ MaximumModuleDelayTimeFor1_35V

| SPD3_LRDIMM_MODULE_DELAY_TIME SPD3_MODULE_LOADREDUCED::MaximumModuleDelayTimeFor1_35V |

93 Maximum Module Delay Time for 1.35 V

◆ MaximumModuleDelayTimeFor1_5V

| SPD3_LRDIMM_MODULE_DELAY_TIME SPD3_MODULE_LOADREDUCED::MaximumModuleDelayTimeFor1_5V |

91 Maximum Module Delay Time for 1.5 V

◆ MdqTerminationDriveStrengthFor1333_1600

| SPD3_LRDIMM_MDQ_TERMINATION_DRIVE_STRENGTH SPD3_MODULE_LOADREDUCED::MdqTerminationDriveStrengthFor1333_1600 |

78 F1RC15 / F1RC14 - Additive Delay for ODT & CKE

◆ MdqTerminationDriveStrengthFor1866_2133

| SPD3_LRDIMM_MDQ_TERMINATION_DRIVE_STRENGTH SPD3_MODULE_LOADREDUCED::MdqTerminationDriveStrengthFor1866_2133 |

84 F1RC15 / F1RC14 - Additive Delay for ODT & CKE

◆ MdqTerminationDriveStrengthFor800_1066

| SPD3_LRDIMM_MDQ_TERMINATION_DRIVE_STRENGTH SPD3_MODULE_LOADREDUCED::MdqTerminationDriveStrengthFor800_1066 |

72 F1RC15 / F1RC14 - Additive Delay for ODT & CKE

◆ MemoryBufferRevisionNumber

| UINT8 SPD3_MODULE_LOADREDUCED::MemoryBufferRevisionNumber |

64 Memory Buffer Revision Number

◆ MinimumModuleDelayTimeFor1_25V

| SPD3_LRDIMM_MODULE_DELAY_TIME SPD3_MODULE_LOADREDUCED::MinimumModuleDelayTimeFor1_25V |

94 Minimum Module Delay Time for 1.25 V

◆ MinimumModuleDelayTimeFor1_35V

| SPD3_LRDIMM_MODULE_DELAY_TIME SPD3_MODULE_LOADREDUCED::MinimumModuleDelayTimeFor1_35V |

92 Minimum Module Delay Time for 1.35 V

◆ MinimumModuleDelayTimeFor1_5V

| SPD3_LRDIMM_MODULE_DELAY_TIME SPD3_MODULE_LOADREDUCED::MinimumModuleDelayTimeFor1_5V |

90 Minimum Module Delay Time for 1.5 V

◆ ModuleMaximumThickness

| SPD3_LRDIMM_MODULE_NOMINAL_THICKNESS SPD3_MODULE_LOADREDUCED::ModuleMaximumThickness |

61 Module Maximum Thickness

◆ ModuleNominalHeight

| SPD3_LRDIMM_MODULE_NOMINAL_HEIGHT SPD3_MODULE_LOADREDUCED::ModuleNominalHeight |

60 Module Nominal Height

◆ MR_1_2RegistersFor1333_1600

| SPD3_LRDIMM_MR_1_2 SPD3_MODULE_LOADREDUCED::MR_1_2RegistersFor1333_1600 |

83 MR1,2 Registers for 800 & 1066

◆ MR_1_2RegistersFor1866_2133

| SPD3_LRDIMM_MR_1_2 SPD3_MODULE_LOADREDUCED::MR_1_2RegistersFor1866_2133 |

89 MR1,2 Registers for 800 & 1066

◆ MR_1_2RegistersFor800_1066

| SPD3_LRDIMM_MR_1_2 SPD3_MODULE_LOADREDUCED::MR_1_2RegistersFor800_1066 |

77 MR1,2 Registers for 800 & 1066

◆ PersonalityByte

| UINT8 SPD3_MODULE_LOADREDUCED::PersonalityByte[116 - 102+1] |

102-116 Memory Buffer Personality Bytes

◆ Rank_0_1QxOdtControlFor1333_1600

| SPD3_LRDIMM_RANK_READ_WRITE_QXODT_CONTROL SPD3_MODULE_LOADREDUCED::Rank_0_1QxOdtControlFor1333_1600 |

79 F[3,4]RC11 / F[3,4]RC10 - Rank 0 & 1 RD & WR QxODT Control for 800 & 1066

◆ Rank_0_1QxOdtControlFor1866_2133

| SPD3_LRDIMM_RANK_READ_WRITE_QXODT_CONTROL SPD3_MODULE_LOADREDUCED::Rank_0_1QxOdtControlFor1866_2133 |

85 F[3,4]RC11 / F[3,4]RC10 - Rank 0 & 1 RD & WR QxODT Control for 800 & 1066

◆ Rank_0_1QxOdtControlFor800_1066

| SPD3_LRDIMM_RANK_READ_WRITE_QXODT_CONTROL SPD3_MODULE_LOADREDUCED::Rank_0_1QxOdtControlFor800_1066 |

73 F[3,4]RC11 / F[3,4]RC10 - Rank 0 & 1 RD & WR QxODT Control for 800 & 1066

◆ Rank_2_3QxOdtControlFor1333_1600

| SPD3_LRDIMM_RANK_READ_WRITE_QXODT_CONTROL SPD3_MODULE_LOADREDUCED::Rank_2_3QxOdtControlFor1333_1600 |

80 F[5,6]RC11 / F[5,6]RC10 - Rank 2 & 3 RD & WR QxODT Control for 800 & 1066

◆ Rank_2_3QxOdtControlFor1866_2133

| SPD3_LRDIMM_RANK_READ_WRITE_QXODT_CONTROL SPD3_MODULE_LOADREDUCED::Rank_2_3QxOdtControlFor1866_2133 |

86 F[5,6]RC11 / F[5,6]RC10 - Rank 2 & 3 RD & WR QxODT Control for 800 & 1066

◆ Rank_2_3QxOdtControlFor800_1066

| SPD3_LRDIMM_RANK_READ_WRITE_QXODT_CONTROL SPD3_MODULE_LOADREDUCED::Rank_2_3QxOdtControlFor800_1066 |

74 F[5,6]RC11 / F[5,6]RC10 - Rank 2 & 3 RD & WR QxODT Control for 800 & 1066

◆ Rank_4_5QxOdtControlFor1333_1600

| SPD3_LRDIMM_RANK_READ_WRITE_QXODT_CONTROL SPD3_MODULE_LOADREDUCED::Rank_4_5QxOdtControlFor1333_1600 |

81 F[7,8]RC11 / F[7,8]RC10 - Rank 4 & 5 RD & WR QxODT Control for 800 & 1066

◆ Rank_4_5QxOdtControlFor1866_2133

| SPD3_LRDIMM_RANK_READ_WRITE_QXODT_CONTROL SPD3_MODULE_LOADREDUCED::Rank_4_5QxOdtControlFor1866_2133 |

87 F[7,8]RC11 / F[7,8]RC10 - Rank 4 & 5 RD & WR QxODT Control for 800 & 1066

◆ Rank_4_5QxOdtControlFor800_1066

| SPD3_LRDIMM_RANK_READ_WRITE_QXODT_CONTROL SPD3_MODULE_LOADREDUCED::Rank_4_5QxOdtControlFor800_1066 |

75 F[7,8]RC11 / F[7,8]RC10 - Rank 4 & 5 RD & WR QxODT Control for 800 & 1066

◆ Rank_6_7QxOdtControlFor1333_1600

| SPD3_LRDIMM_RANK_READ_WRITE_QXODT_CONTROL SPD3_MODULE_LOADREDUCED::Rank_6_7QxOdtControlFor1333_1600 |

82 F[9,10]RC11 / F[9,10]RC10 - Rank 6 & 7 RD & WR QxODT Control for 800 & 1066

◆ Rank_6_7QxOdtControlFor1866_2133

| SPD3_LRDIMM_RANK_READ_WRITE_QXODT_CONTROL SPD3_MODULE_LOADREDUCED::Rank_6_7QxOdtControlFor1866_2133 |

88 F[9,10]RC11 / F[9,10]RC10 - Rank 6 & 7 RD & WR QxODT Control for 800 & 1066

◆ Rank_6_7QxOdtControlFor800_1066

| SPD3_LRDIMM_RANK_READ_WRITE_QXODT_CONTROL SPD3_MODULE_LOADREDUCED::Rank_6_7QxOdtControlFor800_1066 |

76 F[9,10]RC11 / F[9,10]RC10 - Rank 6 & 7 RD & WR QxODT Control for 800 & 1066

◆ ReferenceRawCardUsed

| SPD3_LRDIMM_REFERENCE_RAW_CARD SPD3_MODULE_LOADREDUCED::ReferenceRawCardUsed |

62 Reference Raw Card Used

◆ Reserved

| UINT8 SPD3_MODULE_LOADREDUCED::Reserved[101 - 96+1] |

96-101 Reserved

◆ TimingControlDriveStrengthCaCs

| SPD3_LRDIMM_TIMING_CONTROL_DRIVE_STRENGTH SPD3_MODULE_LOADREDUCED::TimingControlDriveStrengthCaCs |

67 F0RC3 / F0RC2 - Timing Control & Drive Strength, CA & CS

The documentation for this struct was generated from the following file:

- XenevaOS/Boot/include/IndustryStandard/SdramSpdDdr3.h