#include <SdramSpdDdr4.h>

Public Attributes | |

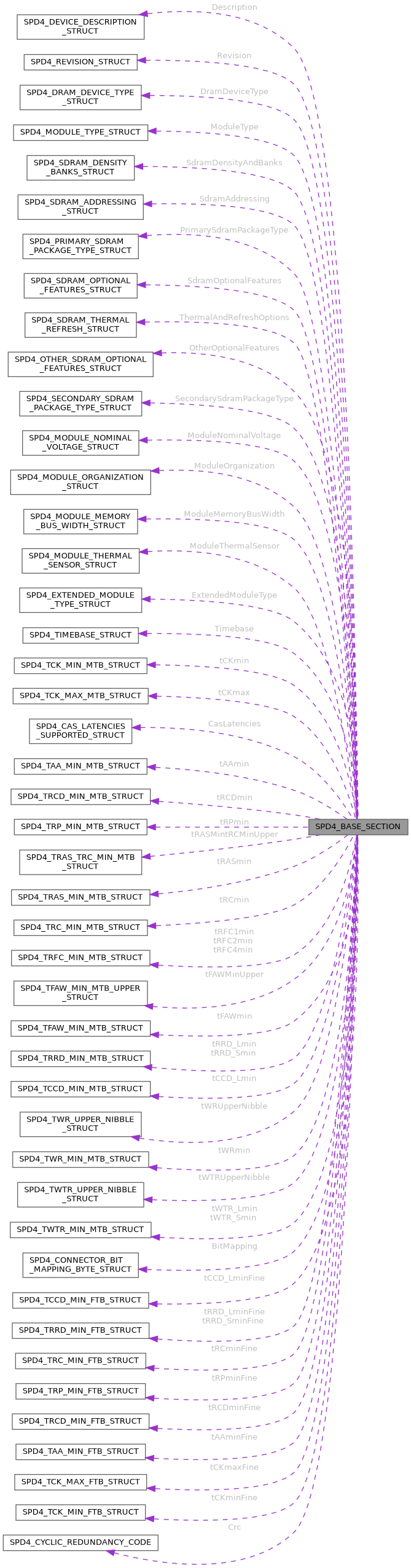

| SPD4_DEVICE_DESCRIPTION_STRUCT | Description |

| 0 Number of Serial PD Bytes Written / SPD Device Size / CRC Coverage 1, 2 | |

| SPD4_REVISION_STRUCT | Revision |

| 1 SPD Revision | |

| SPD4_DRAM_DEVICE_TYPE_STRUCT | DramDeviceType |

| 2 DRAM Device Type | |

| SPD4_MODULE_TYPE_STRUCT | ModuleType |

| 3 Module Type | |

| SPD4_SDRAM_DENSITY_BANKS_STRUCT | SdramDensityAndBanks |

| 4 SDRAM Density and Banks | |

| SPD4_SDRAM_ADDRESSING_STRUCT | SdramAddressing |

| 5 SDRAM Addressing | |

| SPD4_PRIMARY_SDRAM_PACKAGE_TYPE_STRUCT | PrimarySdramPackageType |

| 6 Primary SDRAM Package Type | |

| SPD4_SDRAM_OPTIONAL_FEATURES_STRUCT | SdramOptionalFeatures |

| 7 SDRAM Optional Features | |

| SPD4_SDRAM_THERMAL_REFRESH_STRUCT | ThermalAndRefreshOptions |

| 8 SDRAM Thermal and Refresh Options | |

| SPD4_OTHER_SDRAM_OPTIONAL_FEATURES_STRUCT | OtherOptionalFeatures |

| 9 Other SDRAM Optional Features | |

| SPD4_SECONDARY_SDRAM_PACKAGE_TYPE_STRUCT | SecondarySdramPackageType |

| 10 Secondary SDRAM Package Type | |

| SPD4_MODULE_NOMINAL_VOLTAGE_STRUCT | ModuleNominalVoltage |

| 11 Module Nominal Voltage, VDD | |

| SPD4_MODULE_ORGANIZATION_STRUCT | ModuleOrganization |

| 12 Module Organization | |

| SPD4_MODULE_MEMORY_BUS_WIDTH_STRUCT | ModuleMemoryBusWidth |

| 13 Module Memory Bus Width | |

| SPD4_MODULE_THERMAL_SENSOR_STRUCT | ModuleThermalSensor |

| 14 Module Thermal Sensor | |

| SPD4_EXTENDED_MODULE_TYPE_STRUCT | ExtendedModuleType |

| 15 Extended Module Type | |

| UINT8 | Reserved0 |

| 16 Reserved | |

| SPD4_TIMEBASE_STRUCT | Timebase |

| 17 Timebases | |

| SPD4_TCK_MIN_MTB_STRUCT | tCKmin |

| 18 SDRAM Minimum Cycle Time (tCKmin) | |

| SPD4_TCK_MAX_MTB_STRUCT | tCKmax |

| 19 SDRAM Maximum Cycle Time (tCKmax) | |

| SPD4_CAS_LATENCIES_SUPPORTED_STRUCT | CasLatencies |

| 20-23 CAS Latencies Supported | |

| SPD4_TAA_MIN_MTB_STRUCT | tAAmin |

| 24 Minimum CAS Latency Time (tAAmin) | |

| SPD4_TRCD_MIN_MTB_STRUCT | tRCDmin |

| 25 Minimum RAS# to CAS# Delay Time (tRCDmin) | |

| SPD4_TRP_MIN_MTB_STRUCT | tRPmin |

| 26 Minimum Row Precharge Delay Time (tRPmin) | |

| SPD4_TRAS_TRC_MIN_MTB_STRUCT | tRASMintRCMinUpper |

| 27 Upper Nibbles for tRAS and tRC | |

| SPD4_TRAS_MIN_MTB_STRUCT | tRASmin |

| 28 Minimum Active to Precharge Delay Time (tRASmin), Least Significant Byte | |

| SPD4_TRC_MIN_MTB_STRUCT | tRCmin |

| 29 Minimum Active to Active/Refresh Delay Time (tRCmin), Least Significant Byte | |

| SPD4_TRFC_MIN_MTB_STRUCT | tRFC1min |

| 30-31 Minimum Refresh Recovery Delay Time (tRFC1min) | |

| SPD4_TRFC_MIN_MTB_STRUCT | tRFC2min |

| 32-33 Minimum Refresh Recovery Delay Time (tRFC2min) | |

| SPD4_TRFC_MIN_MTB_STRUCT | tRFC4min |

| 34-35 Minimum Refresh Recovery Delay Time (tRFC4min) | |

| SPD4_TFAW_MIN_MTB_UPPER_STRUCT | tFAWMinUpper |

| 36 Upper Nibble for tFAW | |

| SPD4_TFAW_MIN_MTB_STRUCT | tFAWmin |

| 37 Minimum Four Activate Window Delay Time (tFAWmin) | |

| SPD4_TRRD_MIN_MTB_STRUCT | tRRD_Smin |

| 38 Minimum Activate to Activate Delay Time (tRRD_Smin), different bank group | |

| SPD4_TRRD_MIN_MTB_STRUCT | tRRD_Lmin |

| 39 Minimum Activate to Activate Delay Time (tRRD_Lmin), same bank group | |

| SPD4_TCCD_MIN_MTB_STRUCT | tCCD_Lmin |

| 40 Minimum CAS to CAS Delay Time (tCCD_Lmin), Same Bank Group | |

| SPD4_TWR_UPPER_NIBBLE_STRUCT | tWRUpperNibble |

| 41 Upper Nibble for tWRmin | |

| SPD4_TWR_MIN_MTB_STRUCT | tWRmin |

| 42 Minimum Write Recovery Time (tWRmin) | |

| SPD4_TWTR_UPPER_NIBBLE_STRUCT | tWTRUpperNibble |

| 43 Upper Nibbles for tWTRmin | |

| SPD4_TWTR_MIN_MTB_STRUCT | tWTR_Smin |

| 44 Minimum Write to Read Time (tWTR_Smin), Different Bank Group | |

| SPD4_TWTR_MIN_MTB_STRUCT | tWTR_Lmin |

| 45 Minimum Write to Read Time (tWTR_Lmin), Same Bank Group | |

| UINT8 | Reserved1 [59 - 46+1] |

| 46-59 Reserved | |

| SPD4_CONNECTOR_BIT_MAPPING_BYTE_STRUCT | BitMapping [77 - 60+1] |

| 60-77 Connector to SDRAM Bit Mapping | |

| UINT8 | Reserved2 [116 - 78+1] |

| 78-116 Reserved | |

| SPD4_TCCD_MIN_FTB_STRUCT | tCCD_LminFine |

| 117 Fine Offset for Minimum CAS to CAS Delay Time (tCCD_Lmin), same bank group | |

| SPD4_TRRD_MIN_FTB_STRUCT | tRRD_LminFine |

| 118 Fine Offset for Minimum Activate to Activate Delay Time (tRRD_Lmin), different bank group | |

| SPD4_TRRD_MIN_FTB_STRUCT | tRRD_SminFine |

| 119 Fine Offset for Minimum Activate to Activate Delay Time (tRRD_Smin), same bank group | |

| SPD4_TRC_MIN_FTB_STRUCT | tRCminFine |

| 120 Fine Offset for Minimum Active to Active/Refresh Delay Time (tRCmin) | |

| SPD4_TRP_MIN_FTB_STRUCT | tRPminFine |

| 121 Fine Offset for Minimum Row Precharge Delay Time (tRPabmin) | |

| SPD4_TRCD_MIN_FTB_STRUCT | tRCDminFine |

| 122 Fine Offset for Minimum RAS# to CAS# Delay Time (tRCDmin) | |

| SPD4_TAA_MIN_FTB_STRUCT | tAAminFine |

| 123 Fine Offset for Minimum CAS Latency Time (tAAmin) | |

| SPD4_TCK_MAX_FTB_STRUCT | tCKmaxFine |

| 124 Fine Offset for SDRAM Minimum Cycle Time (tCKmax) | |

| SPD4_TCK_MIN_FTB_STRUCT | tCKminFine |

| 125 Fine Offset for SDRAM Maximum Cycle Time (tCKmin) | |

| SPD4_CYCLIC_REDUNDANCY_CODE | Crc |

| 126-127 Cyclical Redundancy Code (CRC) | |

Member Data Documentation

◆ BitMapping

| SPD4_CONNECTOR_BIT_MAPPING_BYTE_STRUCT SPD4_BASE_SECTION::BitMapping[77 - 60+1] |

60-77 Connector to SDRAM Bit Mapping

◆ CasLatencies

| SPD4_CAS_LATENCIES_SUPPORTED_STRUCT SPD4_BASE_SECTION::CasLatencies |

20-23 CAS Latencies Supported

◆ Crc

| SPD4_CYCLIC_REDUNDANCY_CODE SPD4_BASE_SECTION::Crc |

126-127 Cyclical Redundancy Code (CRC)

◆ Description

| SPD4_DEVICE_DESCRIPTION_STRUCT SPD4_BASE_SECTION::Description |

0 Number of Serial PD Bytes Written / SPD Device Size / CRC Coverage 1, 2

◆ DramDeviceType

| SPD4_DRAM_DEVICE_TYPE_STRUCT SPD4_BASE_SECTION::DramDeviceType |

2 DRAM Device Type

◆ ExtendedModuleType

| SPD4_EXTENDED_MODULE_TYPE_STRUCT SPD4_BASE_SECTION::ExtendedModuleType |

15 Extended Module Type

◆ ModuleMemoryBusWidth

| SPD4_MODULE_MEMORY_BUS_WIDTH_STRUCT SPD4_BASE_SECTION::ModuleMemoryBusWidth |

13 Module Memory Bus Width

◆ ModuleNominalVoltage

| SPD4_MODULE_NOMINAL_VOLTAGE_STRUCT SPD4_BASE_SECTION::ModuleNominalVoltage |

11 Module Nominal Voltage, VDD

◆ ModuleOrganization

| SPD4_MODULE_ORGANIZATION_STRUCT SPD4_BASE_SECTION::ModuleOrganization |

12 Module Organization

◆ ModuleThermalSensor

| SPD4_MODULE_THERMAL_SENSOR_STRUCT SPD4_BASE_SECTION::ModuleThermalSensor |

14 Module Thermal Sensor

◆ ModuleType

| SPD4_MODULE_TYPE_STRUCT SPD4_BASE_SECTION::ModuleType |

3 Module Type

◆ OtherOptionalFeatures

| SPD4_OTHER_SDRAM_OPTIONAL_FEATURES_STRUCT SPD4_BASE_SECTION::OtherOptionalFeatures |

9 Other SDRAM Optional Features

◆ PrimarySdramPackageType

| SPD4_PRIMARY_SDRAM_PACKAGE_TYPE_STRUCT SPD4_BASE_SECTION::PrimarySdramPackageType |

6 Primary SDRAM Package Type

◆ Reserved0

| UINT8 SPD4_BASE_SECTION::Reserved0 |

16 Reserved

◆ Reserved1

| UINT8 SPD4_BASE_SECTION::Reserved1[59 - 46+1] |

46-59 Reserved

◆ Reserved2

| UINT8 SPD4_BASE_SECTION::Reserved2[116 - 78+1] |

78-116 Reserved

◆ Revision

| SPD4_REVISION_STRUCT SPD4_BASE_SECTION::Revision |

1 SPD Revision

◆ SdramAddressing

| SPD4_SDRAM_ADDRESSING_STRUCT SPD4_BASE_SECTION::SdramAddressing |

5 SDRAM Addressing

◆ SdramDensityAndBanks

| SPD4_SDRAM_DENSITY_BANKS_STRUCT SPD4_BASE_SECTION::SdramDensityAndBanks |

4 SDRAM Density and Banks

◆ SdramOptionalFeatures

| SPD4_SDRAM_OPTIONAL_FEATURES_STRUCT SPD4_BASE_SECTION::SdramOptionalFeatures |

7 SDRAM Optional Features

◆ SecondarySdramPackageType

| SPD4_SECONDARY_SDRAM_PACKAGE_TYPE_STRUCT SPD4_BASE_SECTION::SecondarySdramPackageType |

10 Secondary SDRAM Package Type

◆ tAAmin

| SPD4_TAA_MIN_MTB_STRUCT SPD4_BASE_SECTION::tAAmin |

24 Minimum CAS Latency Time (tAAmin)

◆ tAAminFine

| SPD4_TAA_MIN_FTB_STRUCT SPD4_BASE_SECTION::tAAminFine |

123 Fine Offset for Minimum CAS Latency Time (tAAmin)

◆ tCCD_Lmin

| SPD4_TCCD_MIN_MTB_STRUCT SPD4_BASE_SECTION::tCCD_Lmin |

40 Minimum CAS to CAS Delay Time (tCCD_Lmin), Same Bank Group

◆ tCCD_LminFine

| SPD4_TCCD_MIN_FTB_STRUCT SPD4_BASE_SECTION::tCCD_LminFine |

117 Fine Offset for Minimum CAS to CAS Delay Time (tCCD_Lmin), same bank group

◆ tCKmax

| SPD4_TCK_MAX_MTB_STRUCT SPD4_BASE_SECTION::tCKmax |

19 SDRAM Maximum Cycle Time (tCKmax)

◆ tCKmaxFine

| SPD4_TCK_MAX_FTB_STRUCT SPD4_BASE_SECTION::tCKmaxFine |

124 Fine Offset for SDRAM Minimum Cycle Time (tCKmax)

◆ tCKmin

| SPD4_TCK_MIN_MTB_STRUCT SPD4_BASE_SECTION::tCKmin |

18 SDRAM Minimum Cycle Time (tCKmin)

◆ tCKminFine

| SPD4_TCK_MIN_FTB_STRUCT SPD4_BASE_SECTION::tCKminFine |

125 Fine Offset for SDRAM Maximum Cycle Time (tCKmin)

◆ tFAWmin

| SPD4_TFAW_MIN_MTB_STRUCT SPD4_BASE_SECTION::tFAWmin |

37 Minimum Four Activate Window Delay Time (tFAWmin)

◆ tFAWMinUpper

| SPD4_TFAW_MIN_MTB_UPPER_STRUCT SPD4_BASE_SECTION::tFAWMinUpper |

36 Upper Nibble for tFAW

◆ ThermalAndRefreshOptions

| SPD4_SDRAM_THERMAL_REFRESH_STRUCT SPD4_BASE_SECTION::ThermalAndRefreshOptions |

8 SDRAM Thermal and Refresh Options

◆ Timebase

| SPD4_TIMEBASE_STRUCT SPD4_BASE_SECTION::Timebase |

17 Timebases

◆ tRASmin

| SPD4_TRAS_MIN_MTB_STRUCT SPD4_BASE_SECTION::tRASmin |

28 Minimum Active to Precharge Delay Time (tRASmin), Least Significant Byte

◆ tRASMintRCMinUpper

| SPD4_TRAS_TRC_MIN_MTB_STRUCT SPD4_BASE_SECTION::tRASMintRCMinUpper |

27 Upper Nibbles for tRAS and tRC

◆ tRCDmin

| SPD4_TRCD_MIN_MTB_STRUCT SPD4_BASE_SECTION::tRCDmin |

25 Minimum RAS# to CAS# Delay Time (tRCDmin)

◆ tRCDminFine

| SPD4_TRCD_MIN_FTB_STRUCT SPD4_BASE_SECTION::tRCDminFine |

122 Fine Offset for Minimum RAS# to CAS# Delay Time (tRCDmin)

◆ tRCmin

| SPD4_TRC_MIN_MTB_STRUCT SPD4_BASE_SECTION::tRCmin |

29 Minimum Active to Active/Refresh Delay Time (tRCmin), Least Significant Byte

◆ tRCminFine

| SPD4_TRC_MIN_FTB_STRUCT SPD4_BASE_SECTION::tRCminFine |

120 Fine Offset for Minimum Active to Active/Refresh Delay Time (tRCmin)

◆ tRFC1min

| SPD4_TRFC_MIN_MTB_STRUCT SPD4_BASE_SECTION::tRFC1min |

30-31 Minimum Refresh Recovery Delay Time (tRFC1min)

◆ tRFC2min

| SPD4_TRFC_MIN_MTB_STRUCT SPD4_BASE_SECTION::tRFC2min |

32-33 Minimum Refresh Recovery Delay Time (tRFC2min)

◆ tRFC4min

| SPD4_TRFC_MIN_MTB_STRUCT SPD4_BASE_SECTION::tRFC4min |

34-35 Minimum Refresh Recovery Delay Time (tRFC4min)

◆ tRPmin

| SPD4_TRP_MIN_MTB_STRUCT SPD4_BASE_SECTION::tRPmin |

26 Minimum Row Precharge Delay Time (tRPmin)

◆ tRPminFine

| SPD4_TRP_MIN_FTB_STRUCT SPD4_BASE_SECTION::tRPminFine |

121 Fine Offset for Minimum Row Precharge Delay Time (tRPabmin)

◆ tRRD_Lmin

| SPD4_TRRD_MIN_MTB_STRUCT SPD4_BASE_SECTION::tRRD_Lmin |

39 Minimum Activate to Activate Delay Time (tRRD_Lmin), same bank group

◆ tRRD_LminFine

| SPD4_TRRD_MIN_FTB_STRUCT SPD4_BASE_SECTION::tRRD_LminFine |

118 Fine Offset for Minimum Activate to Activate Delay Time (tRRD_Lmin), different bank group

◆ tRRD_Smin

| SPD4_TRRD_MIN_MTB_STRUCT SPD4_BASE_SECTION::tRRD_Smin |

38 Minimum Activate to Activate Delay Time (tRRD_Smin), different bank group

◆ tRRD_SminFine

| SPD4_TRRD_MIN_FTB_STRUCT SPD4_BASE_SECTION::tRRD_SminFine |

119 Fine Offset for Minimum Activate to Activate Delay Time (tRRD_Smin), same bank group

◆ tWRmin

| SPD4_TWR_MIN_MTB_STRUCT SPD4_BASE_SECTION::tWRmin |

42 Minimum Write Recovery Time (tWRmin)

◆ tWRUpperNibble

| SPD4_TWR_UPPER_NIBBLE_STRUCT SPD4_BASE_SECTION::tWRUpperNibble |

41 Upper Nibble for tWRmin

◆ tWTR_Lmin

| SPD4_TWTR_MIN_MTB_STRUCT SPD4_BASE_SECTION::tWTR_Lmin |

45 Minimum Write to Read Time (tWTR_Lmin), Same Bank Group

◆ tWTR_Smin

| SPD4_TWTR_MIN_MTB_STRUCT SPD4_BASE_SECTION::tWTR_Smin |

44 Minimum Write to Read Time (tWTR_Smin), Different Bank Group

◆ tWTRUpperNibble

| SPD4_TWTR_UPPER_NIBBLE_STRUCT SPD4_BASE_SECTION::tWTRUpperNibble |

43 Upper Nibbles for tWTRmin

The documentation for this struct was generated from the following file:

- XenevaOS/Boot/include/IndustryStandard/SdramSpdDdr4.h