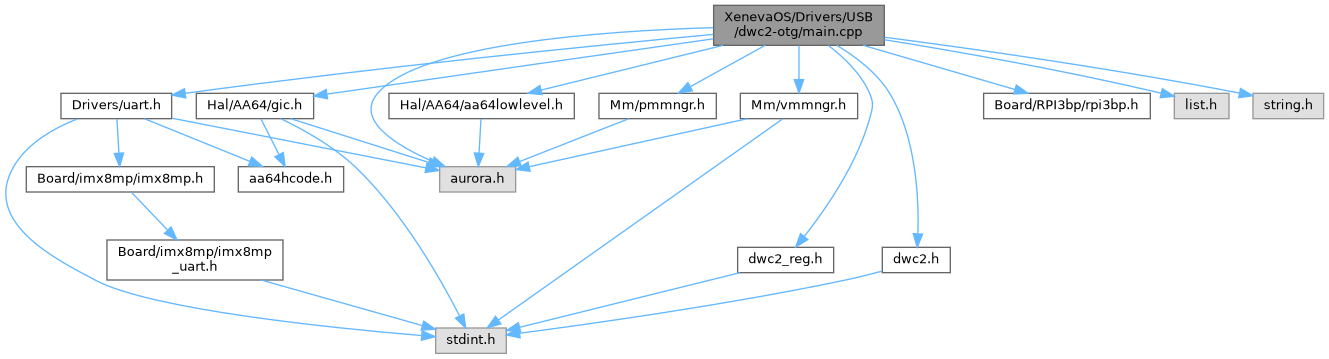

#include <aurora.h>#include <Drivers/uart.h>#include <Mm/vmmngr.h>#include "dwc2_reg.h"#include <Hal/AA64/aa64lowlevel.h>#include <Board/RPI3bp/rpi3bp.h>#include <Hal/AA64/gic.h>#include "dwc2.h"#include <Mm/pmmngr.h>#include <list.h>#include <string.h>

Classes | |

| struct | dwc2_dma_slot |

Macros | |

| #define | DWC2_BASE 0x3F980000 |

| #define | DWC2_GSNPSID 0x40 |

| #define | HPRT_DEFAULT_MASK ((1ULL << 1) | (1ULL << 2) | (1ULL << 3) | (1ULL << 5)) |

| #define | DWC2_SETUP_SLOT 1 |

| #define | DWC2_GAHBCFG_WAIT_AXI_WRITES (1ULL << 4) |

| #define | DWC2_GAHBCFG_MAX_AXI_BURST__MASK (3ULL << 1) |

| #define | DWC2_GAHBCFG_MAX_AXI_BURST__SHIFT 1 |

| #define | DWC2_HWCFG1_FSLS_PCLK_SEL__MASK (3ULL << 0) |

| #define | DWC2_HWCFG1_FSLS_PCLK_SEL_48_MHZ 1 |

| #define | DWC2_HWCFG1_FSLS_PCLK_SEL_30_60_MHZ 0 |

| #define | DMA_ADDRESS 0xFFFFF00000000000 |

Functions | |

| AU_EXTERN AU_EXPORT int | AuDriverUnload () |

| uint32_t | dwc2_read (uint64_t base) |

| dwc2_read – reads a value from dwc2 register | |

| void | dwc2_write (uint64_t base, uint32_t value) |

| dwc2_write – write a value to dwc2 register | |

| void | dwc2_wait_ahb_idle (struct dwc2_core_regs *regs) |

| void | dwc2_core_reset (struct dwc2_core_regs *regs) |

| dwc2_core_reset – reset the otg controller | |

| void | dwc2_config_ahb (struct dwc2_core_regs *regs) |

| void | dwc2_config_usb_phy (struct dwc2_core_regs *regs) |

| void | dwc2_config_fifos (struct dwc2_core_regs *regs) |

| void | dwc2_init_core (struct dwc2_core_regs *regs) |

| void | dwc2_enable_global_interrupt (struct dwc2_core_regs *regs) |

| void | dwc2_flush_tx_fifo (struct dwc2_core_regs *regs, uint32_t nfifo) |

| void | dwc2_flush_rx_fifo (struct dwc2_core_regs *regs) |

| void | dwc2_enable_host_interrupts (struct dwc2_core_regs *regs) |

| void | dwc2_init_host (struct dwc2_core_regs *regs) |

| bool | dwc2_enable_root_port (struct dwc2_core_regs *regs) |

| void | dwc2_interrupt_handler (int spiID) |

| dwc2_interrupt_handler – interrupt handler for dwc2 OTG controller | |

| void | dwc2_initialize (struct dwc2_core_regs *regs) |

| void | dwc2_dump_regs (struct dwc2_core_regs *regs) |

| AU_EXTERN AU_EXPORT int | AuDriverMain () |

| uint64_t | dwc2_get_base () |

| void * | dwc2_get_dma_address () |

| dwc2_get_dma_address – return pre allocated dma address | |

| void * | dwc2_get_dma_address_phys () |

| void | dwc2_add_to_used_dma_list (void *phys) |

| dwc2_add_to_used_dma_list – there is a bug i guess within the dwc2 ip where same buffer can't be used for setup packet | |

| void | dwc2_free_used_dma_list () |

| dwc2_free_used_dma_list – free up all used physical memories, this function must be called at the end of the class driver initialization | |

Variables | |

| uint64_t | _base |

| bool | _root_port_ready |

| bool | _enable_root_port |

| uint64_t * | dmaAddress |

| uint64_t * | dmaAddressPhys |

| uint8_t | port_changed |

Macro Definition Documentation

◆ DMA_ADDRESS

| #define DMA_ADDRESS 0xFFFFF00000000000 |

◆ DWC2_BASE

| #define DWC2_BASE 0x3F980000 |

BSD 2-Clause License

Copyright (c) 2022-2023, Manas Kamal Choudhury All rights reserved.

Redistribution and use in source and binary forms, with or without modification, are permitted provided that the following conditions are met:

- Redistributions of source code must retain the above copyright notice, this list of conditions and the following disclaimer.

- Redistributions in binary form must reproduce the above copyright notice, this list of conditions and the following disclaimer in the documentation and/or other materials provided with the distribution.

THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT HOLDER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

◆ DWC2_GAHBCFG_MAX_AXI_BURST__MASK

| #define DWC2_GAHBCFG_MAX_AXI_BURST__MASK (3ULL << 1) |

◆ DWC2_GAHBCFG_MAX_AXI_BURST__SHIFT

| #define DWC2_GAHBCFG_MAX_AXI_BURST__SHIFT 1 |

◆ DWC2_GAHBCFG_WAIT_AXI_WRITES

| #define DWC2_GAHBCFG_WAIT_AXI_WRITES (1ULL << 4) |

◆ DWC2_GSNPSID

| #define DWC2_GSNPSID 0x40 |

◆ DWC2_HWCFG1_FSLS_PCLK_SEL_30_60_MHZ

| #define DWC2_HWCFG1_FSLS_PCLK_SEL_30_60_MHZ 0 |

◆ DWC2_HWCFG1_FSLS_PCLK_SEL_48_MHZ

| #define DWC2_HWCFG1_FSLS_PCLK_SEL_48_MHZ 1 |

◆ DWC2_HWCFG1_FSLS_PCLK_SEL__MASK

| #define DWC2_HWCFG1_FSLS_PCLK_SEL__MASK (3ULL << 0) |

◆ DWC2_SETUP_SLOT

| #define DWC2_SETUP_SLOT 1 |

◆ HPRT_DEFAULT_MASK

| #define HPRT_DEFAULT_MASK ((1ULL << 1) | (1ULL << 2) | (1ULL << 3) | (1ULL << 5)) |

Function Documentation

◆ AuDriverMain()

This driver is only for RPI for now, and before initializing the driver it is powered up by VideoCore firmware, so life is easy, but for other boards, we need to power it up from their respective power control block

◆ AuDriverUnload()

REFERENCE USED : Linux open source project, U-Boot and USPi from Circle DWC2 regsiter definitions are from mixed sources

◆ dwc2_add_to_used_dma_list()

| void dwc2_add_to_used_dma_list | ( | void * | phys | ) |

dwc2_add_to_used_dma_list – there is a bug i guess within the dwc2 ip where same buffer can't be used for setup packet

◆ dwc2_config_ahb()

| void dwc2_config_ahb | ( | struct dwc2_core_regs * | regs | ) |

dwc2_config_ahb – configure dwc2 ahb

uboot dwc2 code

◆ dwc2_config_fifos()

| void dwc2_config_fifos | ( | struct dwc2_core_regs * | regs | ) |

◆ dwc2_config_usb_phy()

| void dwc2_config_usb_phy | ( | struct dwc2_core_regs * | regs | ) |

◆ dwc2_core_reset()

| void dwc2_core_reset | ( | struct dwc2_core_regs * | regs | ) |

dwc2_core_reset – reset the otg controller

- Parameters

-

regs – pointer to system registers

◆ dwc2_dump_regs()

| void dwc2_dump_regs | ( | struct dwc2_core_regs * | regs | ) |

◆ dwc2_enable_global_interrupt()

| void dwc2_enable_global_interrupt | ( | struct dwc2_core_regs * | regs | ) |

◆ dwc2_enable_host_interrupts()

| void dwc2_enable_host_interrupts | ( | struct dwc2_core_regs * | regs | ) |

◆ dwc2_enable_root_port()

| bool dwc2_enable_root_port | ( | struct dwc2_core_regs * | regs | ) |

◆ dwc2_flush_rx_fifo()

| void dwc2_flush_rx_fifo | ( | struct dwc2_core_regs * | regs | ) |

◆ dwc2_flush_tx_fifo()

| void dwc2_flush_tx_fifo | ( | struct dwc2_core_regs * | regs, |

| uint32_t | nfifo | ||

| ) |

◆ dwc2_free_used_dma_list()

| void dwc2_free_used_dma_list | ( | ) |

dwc2_free_used_dma_list – free up all used physical memories, this function must be called at the end of the class driver initialization

◆ dwc2_get_base()

| uint64_t dwc2_get_base | ( | ) |

◆ dwc2_get_dma_address()

| void * dwc2_get_dma_address | ( | ) |

dwc2_get_dma_address – return pre allocated dma address

◆ dwc2_get_dma_address_phys()

| void * dwc2_get_dma_address_phys | ( | ) |

◆ dwc2_init_core()

| void dwc2_init_core | ( | struct dwc2_core_regs * | regs | ) |

◆ dwc2_init_host()

| void dwc2_init_host | ( | struct dwc2_core_regs * | regs | ) |

restart the phy clock

◆ dwc2_initialize()

| void dwc2_initialize | ( | struct dwc2_core_regs * | regs | ) |

data memory barrier

vendor id check

power on usb hcd via mailbox

disable all global interrupt in gahbcfg

connect irq handler

core init

global irq init

initialize the host

root port enumeration

◆ dwc2_interrupt_handler()

| void dwc2_interrupt_handler | ( | int | spiID | ) |

dwc2_interrupt_handler – interrupt handler for dwc2 OTG controller

- Parameters

-

spiID – system passed interrupt id

PORT interrupt

handle host channel interrupts here

◆ dwc2_read()

dwc2_read – reads a value from dwc2 register

- Parameters

-

base – memory base

◆ dwc2_wait_ahb_idle()

| void dwc2_wait_ahb_idle | ( | struct dwc2_core_regs * | regs | ) |

◆ dwc2_write()

dwc2_write – write a value to dwc2 register

- Parameters

-

base – memory base value – value to write

Variable Documentation

◆ _base

| uint64_t _base |

◆ _enable_root_port

| bool _enable_root_port |

◆ _root_port_ready

| bool _root_port_ready |

◆ dmaAddress

| uint64_t* dmaAddress |

◆ dmaAddressPhys

| uint64_t* dmaAddressPhys |

◆ port_changed

|

extern |